# ICs for Communications

Multichannel Network Interface Controller for HDLC + Extensions MUNICH128X

PEB 20324 Version 2.2

Hardware Reference Manual 04.99

| PEB 20324, PEF 20324             |                                 |                                              |  |  |

|----------------------------------|---------------------------------|----------------------------------------------|--|--|

| Revision History:                |                                 | Current Version: 04.99                       |  |  |

| Previous Version:                |                                 | Product Overview 12/97 DS3                   |  |  |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |  |

| Chapter 6                        | Chapter 5                       | Updated.                                     |  |  |

| Tables 18                        | Tables 2-1<br>2-8               | Pin Description Tables updated.              |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Siemens AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 04.99 Published by Infineon Technologies AG i. Gr., SC, Balanstraße 73, 81541 München

© Infineon Technologies AG i.Gr. 1999. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# Preface

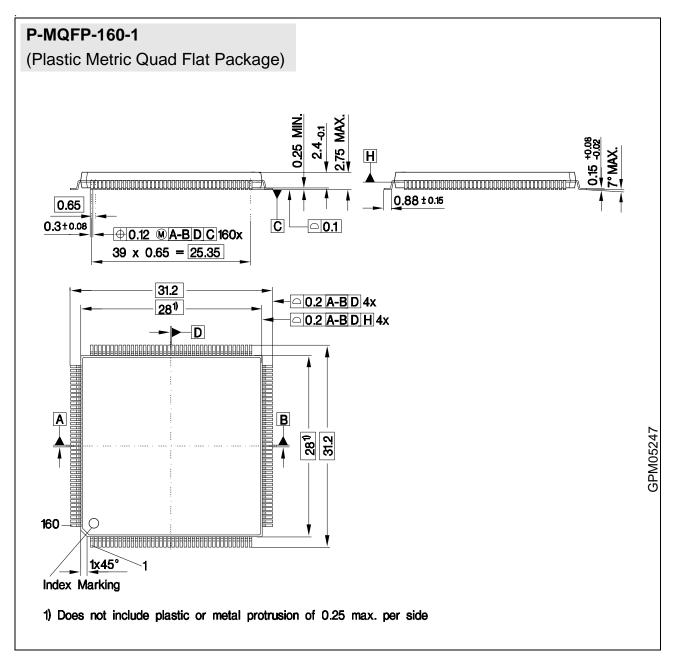

The MUNICH128X is a 128-channel WAN Protocol Controller which provides four independent 24/32-channel HDLC controllers, each with a dedicated 64-channel DMA Controller and a Serial PCM Interface Controller. The device is offered in a 160-pin MQFP package, making it ideal for high-port-density applications.

# **Organization of this Document**

This Hardware Reference Manual is divided into 7 chapters. It is organized as follows:

- Chapter 1, Introduction Gives a general description of the product and its family, lists the key features, and presents some typical applications.

- Chapter 2, Pin Description Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

- Chapter 3, Functional IC Description Gives a general functional overview of the MUNICH128X.

- Chapter 4, Electrical Characteristics Gives a detailed description of all electrical DC and AC characteristics and provides timing diagrams and values for all interfaces.

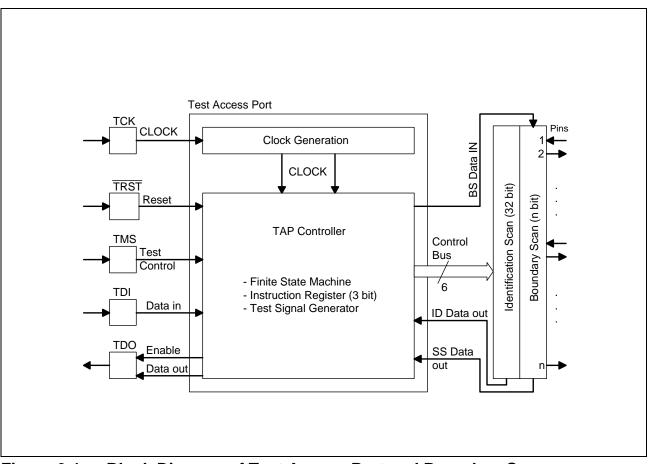

- Chapter 5, Test Modes Gives a detailed description of the JTAG boundary scan interface.

- Chapter 6, Package Outline

# **Related Documentation**

MUNICH128X Version 2.2 Prpgrammer's Reference Manual 03.99 DS1

**Table of Contents**

# PEB 20324 PEF 20324

Page

| 7                                                                                                                                         | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>6</b><br>6.1                                                                                                                           | Test Modes.57Boundary Scan Unit.57                                                                                                                                                                                                                                                                                                                                                                       |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.6.1<br>5.6.1.1<br>5.6.1.2<br>5.6.1.3<br>5.6.2<br>5.6.3<br>5.6.3<br>5.6.4<br>5.6.5 | Electrical Characteristics.37Important Electrical Requirements.37Thermal Package Characteristics.39Operating Range.40DC Characteristics.41Capacitances.42AC Characteristics.43PCI Bus Interface Timing.44PCI Read Transaction.45PCI Write Transaction.47PCI Timing Characteristics.48De-multiplexed Bus Interface.51PCM Serial Interface Timing.53System Interface Timing.55JTAG-Boundary Scan Timing.56 |

| <b>4</b><br>4.1                                                                                                                           | Operational Description                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                                                      | Functional Description.28Functional Overview.28Block Diagram.28Functional Blocks.29System Integration.34                                                                                                                                                                                                                                                                                                 |

| <b>2</b><br>2.1                                                                                                                           | Pin Descriptions.15Pin Diagram.15                                                                                                                                                                                                                                                                                                                                                                        |

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4                                                                                                      | Introduction.7Features.8Logic Symbol.11Typical Applications.12Differences to the MUNICH32.14                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                           | Preface                                                                                                                                                                                                                                                                                                                                                                                                  |

| List of Figur | es                                                            | Page |

|---------------|---------------------------------------------------------------|------|

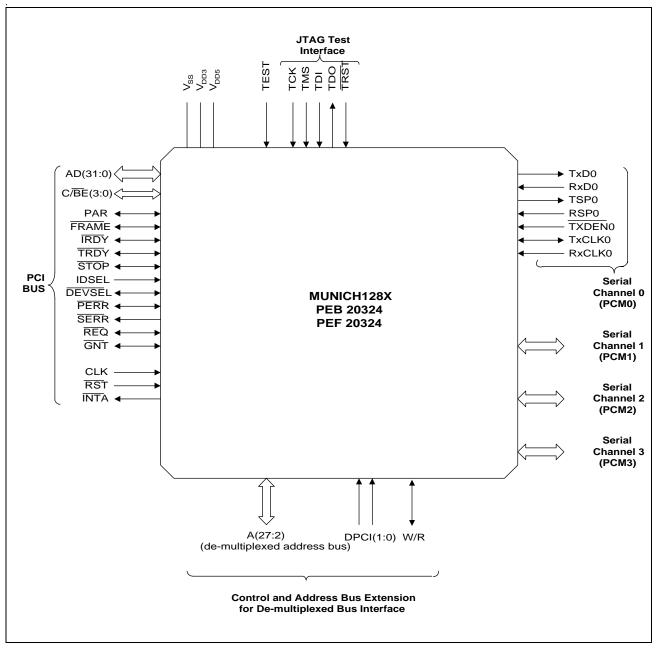

| Figure 1-1    | Simplified Block Diagram                                      | 7    |

| Figure 1-2    | Logic Symbol                                                  |      |

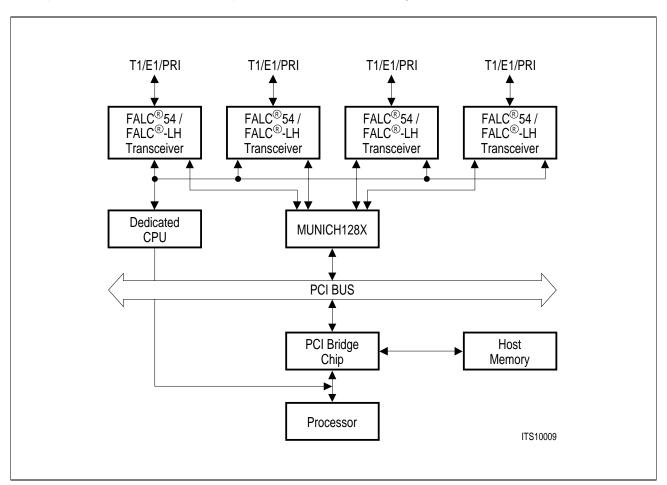

| Figure 1-3    | System Integration of the MUNICH128X in PCI-Based System      | 12   |

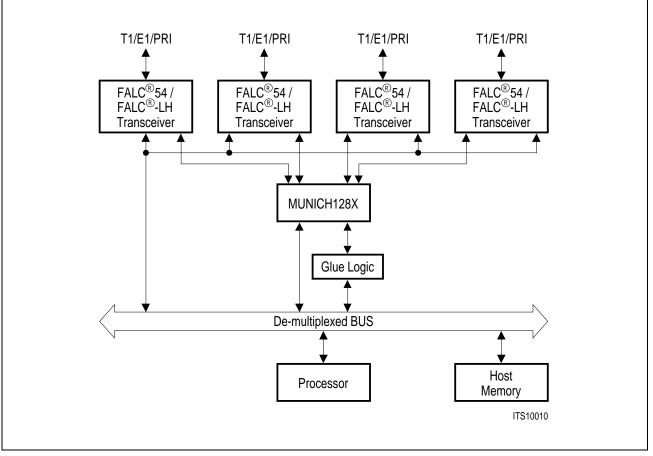

| Figure 1-4    | System Integration of the MUNICH128X in De-multiplexed System | 13   |

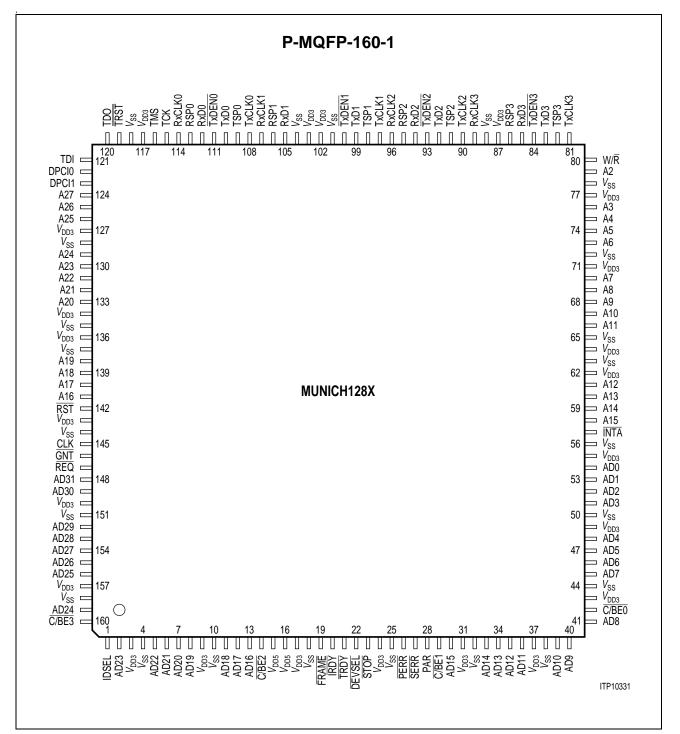

| Figure 2-1    | Pin Configuration                                             | 15   |

| Figure 3-1    | Block Diagram                                                 | 28   |

| Figure 3-1    | System Integration of the MUNICH128X in PCI-Based System      | 34   |

| Figure 3-2    | System Integration of the MUNICH128X in De-multiplexed System | 35   |

| Figure 5-1    | Power-up and Power-down scenarios                             | 37   |

| Figure 5-2    | Power-Failure scenarios                                       | 38   |

| Figure 5-1    | Input/Output Waveform for AC Tests                            | 43   |

| Figure 5-2    | PCI Output Timing Measurement Waveforms                       | 44   |

| Figure 5-3    | PCI Input Timing Measurement Waveforms                        | 44   |

| Figure 5-4    | PCI Read Transaction                                          | 46   |

| Figure 5-5    | PCI Write Transaction                                         | 47   |

| Figure 5-6    | PCI Clock Specification                                       | 49   |

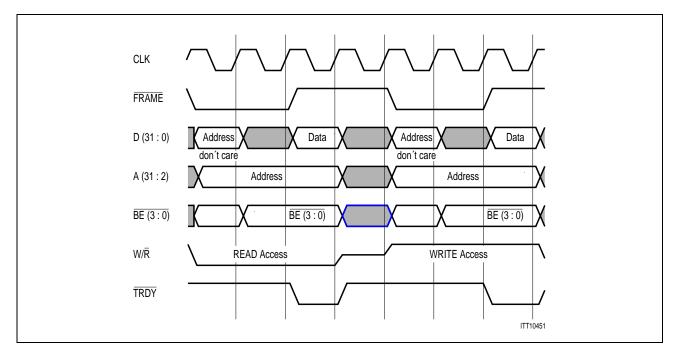

| Figure 5-7    | Master Single READ Transaction followed by a Master Single    |      |

|               | WRITE Transaction in De-multiplexed Bus Configuration         | 51   |

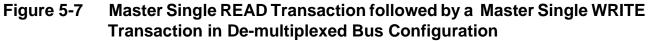

| Figure 5-8    | Master Burst WRITE/READ Access in De-multiplexed Bus          |      |

|               | Configuration                                                 | 51   |

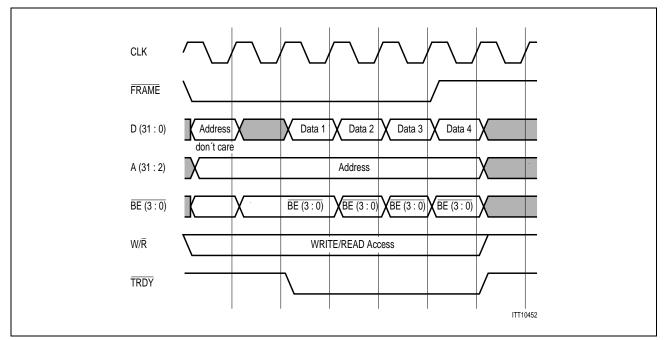

| Figure 5-9    | PCM Serial Interface Timing                                   | 53   |

| Figure 5-10   | System Interface Timing                                       | 55   |

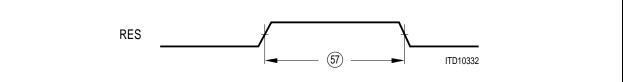

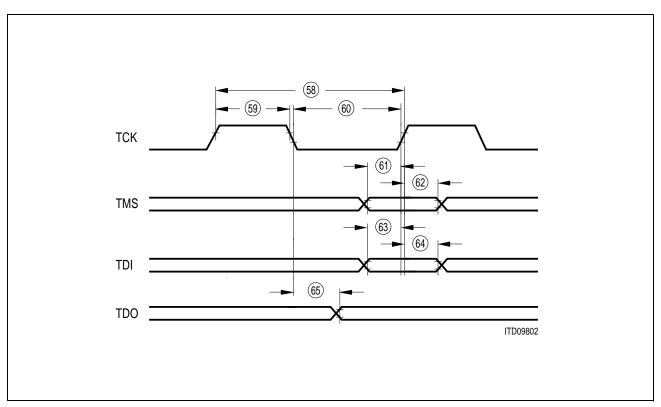

| Figure 5-11   | JTAG-Boundary Scan Timing                                     |      |

| Figure 6-1    | Block Diagram of Test Access Port and Boundary Scan           | 57   |

# List of Tables

# Page

| Table 2-1  | Pin Descriptions by Functional Block: Port 0 Serial Interface                            | 17 |

|------------|------------------------------------------------------------------------------------------|----|

| Table 2-2  | Pin Descriptions by Functional Block: Port 1 Serial Interface                            | 18 |

| Table 2-3  | Pin Descriptions by Functional Block: Port 2 Serial Interface                            | 19 |

| Table 2-4  | Pin Descriptions by Functional Block: Port 3 Serial Interface                            | 20 |

| Table 2-5  | Pin Descriptions by Functional Block: PCI Interface                                      | 21 |

| Table 2-6  | Pin Descriptions by Functional Block:                                                    |    |

|            | DEMUX Interface (additional signals to PCI Interface)                                    | 25 |

| Table 2-7  | Pin Descriptions by Functional Block: Power Supply                                       | 26 |

| Table 2-8  | Pin Descriptions by Functional Block: Test Interface                                     | 27 |

| Table 5-1  | Absolute Maximum Ratings                                                                 | 39 |

| Table 5-2  | Thermal Package Characteristics                                                          | 39 |

| Table 5-3  | Non-PCI Interface Pins                                                                   |    |

|            | TA = 0 to + 70×C; VDD5 = 5 V $\pm$ 5%, VDD3 = 3.3 V $\pm$ 0.3 V,                         |    |

|            | VSS = 0 V                                                                                | 41 |

| Table 5-4  | Non-PCI Interface Pins                                                                   |    |

|            | TA = $25 \times C$ ; VDD5 = 5 V ± 5%, VDD3 = $3.3 \times U \pm 0.3 \times V$ , VSS = 0 V | 42 |

| Table 5-5  | PCI Input and Output Measurement Conditions                                              | 44 |

| Table 5-6  | Number of Wait States Inserted by the MUNICH128X as Initiator                            | 48 |

| Table 5-7  | Number of Wait States Inserted by the MUNICH128X as Slave                                |    |

| Table 5-8  | PCI Clock Characteristics                                                                |    |

| Table 5-9  | PCI Interface Signal Characteristics                                                     | 50 |

| Table 5-10 | Additional De-multiplexed Interface Signal Characteristics                               | 52 |

| Table 5-11 | PCM Serial Interface Timing                                                              | 54 |

| Table 5-12 | System Interface Timing                                                                  | 55 |

| Table 5-13 | JTAG-Boundary Scan Timing                                                                | 56 |

| Table 6-1  | Boundary Scan Sequence in MUNICH128X                                                     | 58 |

| Table 6-2  | Boundary Scan Test Modes                                                                 | 62 |

#### Introduction

# 1 Introduction

The MUNICH128X is a 128-channel WAN Protocol Controller which provides four independent 24/32-channel HDLC controllers, each with a dedicated 64-channel DMA Controller and a Serial PCM Interface Controller. The device is offered in a 160-pin MQFP package, making it ideal for high-port-density applications.

The MUNICH128X provides capability for up to 128 full duplex serial PCM channels. The chip performs layer 2 HDLC formatting/deformatting or V.110 or X.30 protocols up to a data rate of 38.4 kbit/s (V.110) or 64 kbit/s (HDLC). The MUNICH128X also performs transparent transmission for DMI modes 0, 1, and 2. Processed data is transferred to host memory via the PCI interface or de-multiplexed bus interface.

The MUNICH128X is compatible with the LAPD ISDN (Integrated Services Digital Network) protocol specified by CCITT, as well as with HDLC, SDLC, LAPB and DMI protocols. It provides rate adaptation for time slot transmission from 64 kbit/s down to 8 kbit/s and the concatenation of time slots, supporting the ISDN H0, H11, H12 superchannels.

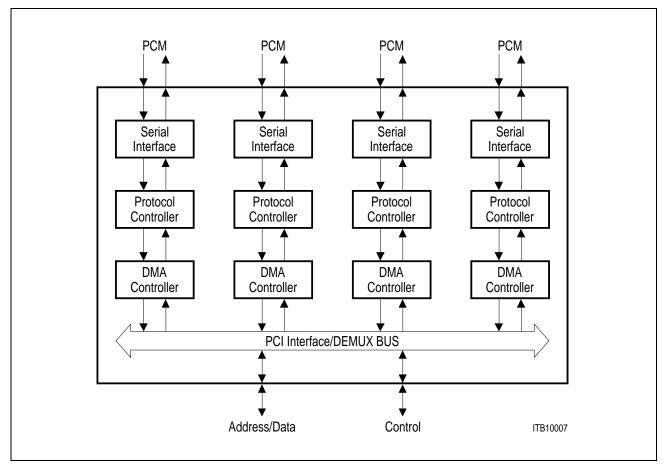

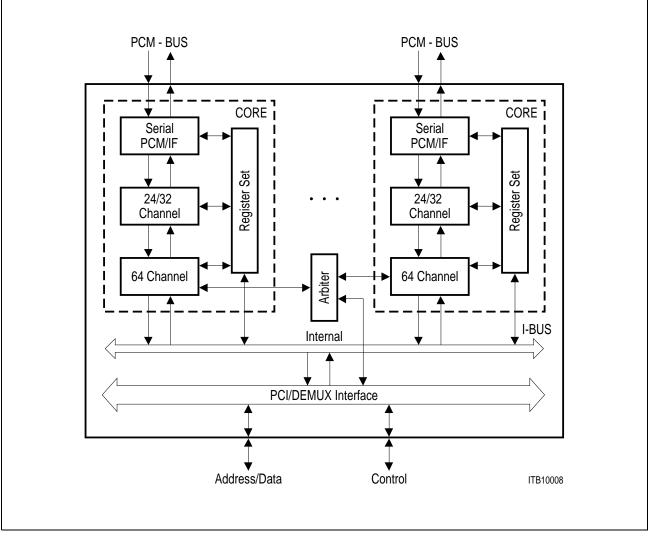

Figure 1-1 Simplified Block Diagram

# Multichannel Network Interface Controller for HDLC + PEB 20324 Extensions MUNICH128X

Version 2.2

# 1.1 Features

Four independent 24/32-channel HDLC PCM Controllers with common PCI interface.

# Each of them provides:

- Dedicated 1024 byte Tx Buffer

- Dedicated 1024 byte Rx Buffer

- Dedicated Serial PCM Interface Controller

- T1 rates: 1.536, 1.544, 3.088, 6.176 Mbit/s

- E1 rates: 2.048, 4.096, 8.192 Mbit/s

- Dedicated 64-channel DMA Controller

- Supports linked-list buffer processing

- 16-DWord Tx DMA FIFO

- 16-DWord Rx DMA FIFO

- 4-DWord burst of Rx descriptors

- 3-DWord burst of Tx descriptors

- n-DWord burst of configuration blocks (n is unlimited according the MUNICH128X, but internal port arbitration may lead to a lower typical burst size of 4 or 8 DWords)

- Dynamic Programmable Channel Allocation

- Compatible with T1/DS1 24-channel and CEPT 32-channel PCM byte format

- Concatenation of any, not necessarily consecutive, time slots to superchannels independently for receive and transmit direction

- Support of H0, H11, H12 ISDN-channels

- Subchanneling on each time slot possible

| Туре      | Package      |

|-----------|--------------|

| PEB 20324 | P-MQFP-160-1 |

| PEF 20324 | P-MQFP-160-1 |

CMOS

#### Introduction

- Bit Processor Functions (adjustable for each channel)

- HDLC Protocol

- Automatic flag detection

- Shared opening and closing flag

- Detection of interframe-time-fill change, generation of interframe-time-fill '1's or flags

- Zero bit insertion

- Flag stuffing and flag adjustment for rate adaption

- CRC generation and checking (16 or 32 bits)

- Transparent CRC option per channel and/or per message

- Error detection (abort, long frame, CRC error, 2 categories of short frames, non-octet frame content)

- ABORT/IDLE flag generation

- V.110/X.30 Protocol

- Automatic synchronization in receive direction, automatic generation of the synchronization pattern in transmit direction

- E/S/X bits freely programmable in transmit direction, may be changed during transmission; changes monitored and reported in receive direction

- Generation/detection of loss of synchronism

- Bit framing with network data rates from 600 bit/s up to 38.4 Kbit/s

- Transparent Mode A

- Slot synchronous transparent transmission/reception without frame structure

- Flag generation, flag stuffing, flag extraction, flag generation in the abort case with programmable flag

- Synchronized data transfer for fractional T1/PRI channels

- Transparent Mode B

- Transparent transmission/reception in frames delimited by 00<sub>H</sub> flags

- Shared opening and closing flag

- Flag stuffing, flag detection, flag generation in the abort case

- Error detection (non octet frame content, short frame, long frame)

- Transparent Mode R

- Transparent transmission/reception with GSM 08.60 frame structure

- Automatic 0000<sub>H</sub> flag generation/detection

- Support of 40,  $39^{1}/_{2}$ ,  $40^{1}/_{2}$  octet frames

- Error detection (non octet frame contents, short frame, long frame)

- Protocol Independent

- Channel inversion (data, flags, IDLE code)

- Format conventions as in CCITT Q.921 § 2.8

- Data over- and underflow detected

#### Introduction

- 32 Bit / 33 MHz PCI 2.1 Interface

- 32 Bit / 33 MHz De-multiplexed Bus Interface Option

- 0.5 µm, 3.3 V-Optimized Technology

- 3.3 V I/O Capability with 5.0 V Input Tolerance

- 160-pin MQFP Package

Introduction

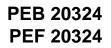

# 1.2 Logic Symbol

Figure 1-2 Logic Symbol

#### Introduction

# 1.3 Typical Applications

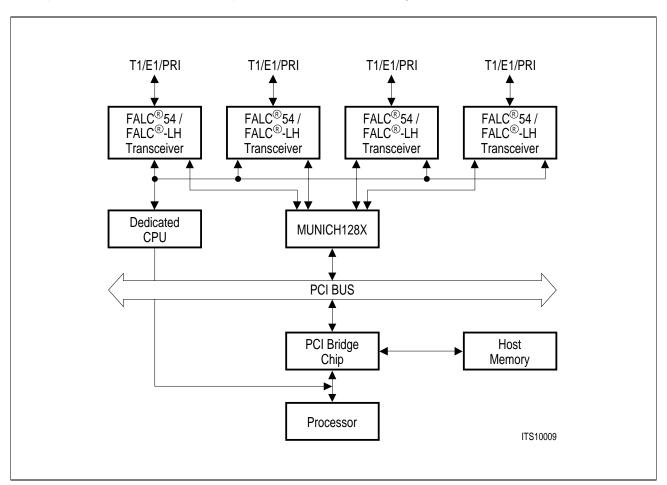

The MUNICH128X provides protocol processing and host memory buffer management for four independent T1/E1 PRI ports. As such, the MUNICH128X fits into a system between the framer or LIU/framer devices (e.g., the Siemens FALC<sup>®</sup>54/FALC<sup>®</sup>54-LH transceiver) and the host bus (e.g. PCI Bus), as illustrated in Figure 1-3.

The MUNICH128X provides four independent Serial PCM ports which connect directly into the framer devices. In PCI based systems a dedicated microcontroller or PCI bridge chip is necessary to configure the framer or LIU/framer devices.

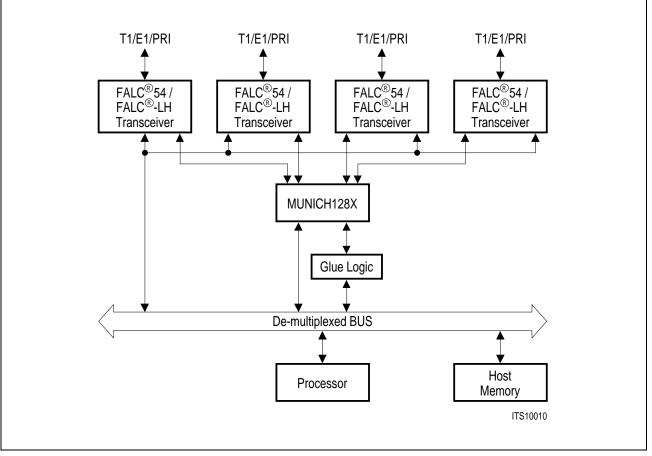

Additionally, the MUNICH128X provides a PCI 2.1 interface which connects directly to the system PCI bus. Optionally, this bus can be configured in De-multiplexed Mode.

Figure 1-3 System Integration of the MUNICH128X in PCI-Based System

#### Introduction

Figure 1-4 System Integration of the MUNICH128X in De-multiplexed System

# Infineon

#### Introduction

# 1.4 Differences to the MUNICH32

- 128-channel capability

- Symmetrical Rx and Tx Buffer Descriptor formats for faster switching

- Improved Tx idle channel polling process for significantly reducing bus occupancy of idle Tx channels

- Dedicated 1024 byte Tx Buffer

- Dedicated 1024 byte Rx Buffer

- Burst capability also on transmit and receive data sections (8 DWORDs)

- Additional PCM modes supported: 3.088 MBit/s, 6.176 MBit/s, 8.192 MBit/s

- 32 Bit / 33 MHz PCI 2.1 master/slave interface; this interface can be configured in De-mux mode

- Separate Rx and Tx Status Queues in host memory (the MUNICH128X provides one set for each of the four HDLC Controllers)

- Slave access to on-chip registers

- Time Slot-shift capability:

- Programmable from -4 clock edges to +3 clock edges relative to the synchronization pulse

- Programmable to sample Tx and/or Rx data at either falling or rising edge of clock

- Software initiated action request (via the Command Register)

- Tx End-of-Packet transmitted-on-wire interrupt capability for each channel

- Tx packet size increased to 64 Kbytes (HDLC mode)

- Rx packet size 8 Kbyte limit interrupt disable

- Tx data TRISTATE<sup>™</sup> control line

- Synchronized data transfer in TMA mode for complete transparency when using fractional T1/PRI

- Little/Big Endian data formats

#### **Pin Descriptions**

# 2 Pin Descriptions

# 2.1 Pin Diagram

(top view)

Figure 2-1 Pin Configuration

#### **Pin Descriptions**

Pin descriptions in **Tables 2-1** to **2-8** are grouped by functional block, as shown by the heading for that group. Pin types are indicated by abbreviations:

# Signal Type Definitions:

The following signal type definitions are partly taken from the PCI Specification Revision 2.1:

| I        | Input is a standard input-only signal.                                                                                                                                                            |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0        | Totem Pole Output is a standard active driver.                                                                                                                                                    |  |  |  |

| t/s, I/O | <i>Tri-State</i> or $I/O$ is a bi-directional, tri-state input/output pin.                                                                                                                        |  |  |  |

| s/t/s    | <i>Sustained Tri-State</i> is an active low tri-state signal owned and driven<br>by one and only one agent at a time. (For further information refer to<br>the PCI Specification Revision 2.1)    |  |  |  |

| o/d      | <i>Open Drain</i> allows multiple devices to share as a wire-OR. A pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |  |  |  |

# Signal Name Conventions:

- NC Not Connected Pin Such pins are not bonded with the silicon. Although any potential at these pins will not impact the device it is recommended to leave them unconnected. NC pins might be used for additional functionality in later versions of the device. Leaving them unconnected will guarentee hardware compatibility to later device versions.

- **Reserved** pins are for vendor specific use only and should be connected as recommended to guarantee normal operation.

- Note: The signal type definition specifies the functional usage of a pin. This does not reflect necessarily the implementation of a pin, e.g. a pin defined of signal type 'Input' may be implemented with a bidirectional pad.

- Note: All unused input or I/O pins without internal Pull-Up/Down resistor must be connected to a defined level either connected to  $V_{DD3}/V_{SS}$  or to a Pull-Up/Down resistor (<= 10k).

| Pin No. | Symbol | Туре | Description                                                                                                                                                                                                                                                           |

|---------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114     | RxCLK0 | I    | Receive Clock 0<br>The clock input pin used for sampling the data on<br>RxD0. The MUNICH128X supports the following PCM<br>clock rates; programmed via the MODE1 register:<br>T1: 1.536 MHz, 1.544 MHz, 3.088 MHz, 6.176 MHz;<br>E1: 2.048 MHz, 4.096 MHz, 8.192 MHz. |

| 112     | RxD0   | I    | <b>Receive Data 0</b><br>The data input pin which is sampled using RxCLK0.                                                                                                                                                                                            |

| 113     | RSP0   | I    | <b>Receive Synchronization Pulse 0</b><br>The input pin used for Rx PCM frame synchronization;<br>the synchronization pulse marks the <i>first</i> bit in the<br>PCM frame.                                                                                           |

| 108     | TxCLK0 | 1    | <b>Transmit Clock 0</b><br>The clock input used for clocking out the data on<br>TxD0. In most applications, the signal that drives this<br>pin is externally connected to RxCLK0.                                                                                     |

| 110     | TxD0   | 0    | Transmit Data 0<br>Provides the data which is clocked out of the<br>MUNICH128X by TxCLK0; data is push-pull for active<br>bits in the PCM frame and TRISTATE <sup>™</sup> for inactive<br>bits.                                                                       |

| 109     | TSP0   | I    | <b>Transmit Synchronization Pulse 0</b><br>The input pin used for Tx PCM frame synchronization;<br>the synchronization pulse marks the <i>last</i> bit in the<br>PCM frame.                                                                                           |

| 111     | TxDEN0 | 0    | <b>Transmit Data Enable 0</b><br>An active low output signal which specifies data on the TxD0 output pin is valid.                                                                                                                                                    |

# **Pin Descriptions**

# Table 2-2 Pin Descriptions by Functional Block: Port 1 Serial Interface

| Pin No. | Symbol | Туре | Description                                                                                                                                                                                                                                                          |

|---------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 107     | RxCLK1 | I    | Receive Clock 1<br>The clock input pin used for sampling the data on<br>RxD1 The MUNICH128X supports the following PCM<br>clock rates, programmed via the MODE1 register:<br>T1: 1.536 MHz, 1.544 MHz, 3.088 MHz, 6.176 MHz;<br>E1: 2.048 MHz, 4.096 MHz, 8.192 MHz. |

| 105     | RxD1   | 1    | <b>Receive Data 1</b><br>The data input pin which is sampled using RxCLK1.                                                                                                                                                                                           |

| 106     | RSP1   | I    | <b>Receive Synchronization Pulse 1</b><br>The input pin used for Rx PCM frame synchronization;<br>the synchronization pulse marks the <i>first</i> bit in the<br>PCM frame.                                                                                          |

| 97      | TxCLK1 | I    | <b>Transmit Clock 1</b><br>The clock input used for clocking out the data on<br>TxD1. In most applications, the signal that drives this<br>pin is externally connected to RxCLK1.                                                                                    |

| 99      | TxD1   | 0    | Transmit Data 1<br>Provides the data which is clocked out of the<br>MUNICH128X by TxCLK1; data is push-pull for active<br>bits in the PCM frame and TRISTATE <sup>™</sup> for inactive<br>bits.                                                                      |

| 98      | TSP1   | I    | <b>Transmit Synchronization Pulse 1</b><br>The input pin used for Tx PCM frame synchronization;<br>the synchronization pulse marks the <i>last</i> bit in the<br>PCM frame.                                                                                          |

| 100     | TxDEN1 | 0    | <b>Transmit Data Enable 1</b><br>An active low output signal which specifies data on the TxD1 output pin is valid.                                                                                                                                                   |

# **Pin Descriptions**

# Table 2-3 Pin Descriptions by Functional Block: Port 2 Serial Interface

| Pin No. | Symbol | Туре | Description                                                                                                                                                                                                                                                           |

|---------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 96      | RxCLK2 | I    | Receive Clock 2<br>The clock input pin used for sampling the data on<br>RxD2. The MUNICH128X supports the following PCM<br>clock rates, programmed via the MODE1 register:<br>T1: 1.536 MHz, 1.544 MHz, 3.088 MHz, 6.176 MHz;<br>E1: 2.048 MHz, 4.096 MHz, 8.192 MHz. |

| 94      | RxD2   | I    | <b>Receive Data 2</b><br>The data input pin which is sampled using RxCLK2.                                                                                                                                                                                            |

| 95      | RSP2   | 1    | <b>Receive Synchronization Pulse 2</b><br>The input pin used for Rx PCM frame synchronization;<br>the synchronization pulse marks the <i>first</i> bit in the<br>PCM frame.                                                                                           |

| 90      | TxCLK2 | I    | <b>Transmit Clock 2</b><br>The clock input used for clocking out the data on<br>TxD2. In most applications, the signal that drives this<br>pin is externally connected to RxCLK2.                                                                                     |

| 92      | TxD2   | 0    | <b>Transmit Data 2</b><br>Provides the data which is clocked out of the<br>MUNICH128X by TxCLK2; data is push-pull for active<br>bits in the PCM frame and TRISTATE <sup>™</sup> for inactive<br>bits.                                                                |

| 91      | TSP2   | 1    | <b>Transmit Synchronization Pulse 2</b><br>The input pin used for Tx PCM frame synchronization;<br>the synchronization pulse marks the <i>last</i> bit in the<br>PCM frame.                                                                                           |

| 93      | TxDEN2 | 0    | <b>Transmit Data Enable 2</b><br>An active low output signal which specifies data on the TxD2 output pin is valid.                                                                                                                                                    |

# **Pin Descriptions**

# Table 2-4 Pin Descriptions by Functional Block: Port 3 Serial Interface

| Pin No. | Symbol | Туре | Description                                                                                                                                                                                                                                                           |

|---------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 89      | RxCLK3 | I    | Receive Clock 3<br>The clock input pin used for sampling the data on<br>RxD3. The MUNICH128X supports the following PCM<br>clock rates, programmed via the MODE1 register:<br>T1: 1.536 MHz, 1.544 MHz, 3.088 MHz, 6.176 MHz;<br>E1: 2.048 MHz, 4.096 MHz, 8.192 MHz. |

| 85      | RxD3   | I    | <b>Receive Data 3</b><br>The data input pin which is sampled using RxCLK3.                                                                                                                                                                                            |

| 86      | RSP3   | I    | <b>Receive Synchronization Pulse 3</b><br>The input pin used for Rx PCM frame synchronization;<br>the synchronization pulse marks the <i>first</i> bit in the<br>PCM frame.                                                                                           |

| 81      | TxCLK3 | I    | <b>Transmit Clock 3</b><br>The clock input used for clocking out the data on<br>TxD3. In most applications, the signal that drives this<br>pin is externally connected to RxCLK3.                                                                                     |

| 83      | TxD3   | 0    | <b>Transmit Data 3</b><br>Provides the data which is clocked out of the<br>MUNICH128X by TxCLK3; data is push-pull for active<br>bits in the PCM frame and TRISTATE <sup>™</sup> for inactive<br>bits.                                                                |

| 82      | TSP3   | I    | <b>Transmit Synchronization Pulse 3</b><br>The input pin used for Tx PCM frame synchronization;<br>the synch. pulse marks the <i>last</i> bit in the PCM frame.                                                                                                       |

| 84      | TxDEN3 | 0    | <b>Transmit Data Enable 3</b><br>An active low output signal which specifies data on the TxD3 output pin is valid.                                                                                                                                                    |

| Pin No.                                                                                | Symbol            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 58,<br>1113, 30,<br>3336,<br>3941,<br>4548,<br>5154,<br>148, 149,<br>152156,<br>159 | AD(31:0)          | t/s  | Address/Data Bus<br>A bus transaction consists of an address phase<br>followed by one or more data phases.<br>When MUNICH128X is Master, AD(31:0) are outputs<br>in the address phase of a transaction. During the data<br>phases, AD(31:0) remain outputs for write<br>transactions, and become inputs for read<br>transactions.<br>When MUNICH128X is Slave, AD(31:0) are inputs in<br>the address phase of a transaction. During the data<br>phases, AD(31:0) remain inputs for write transactions,<br>and become outputs for read transactions.<br>AD(31:0) is sampled on the rising edge of CLK.                     |

| 14, 29, 42,<br>160                                                                     | <u>C/BE</u> (3:0) | t/s  | <b>Command/Byte Enable</b><br>During the address phase of a transaction, $\overline{C/BE}(3:0)$<br>define the bus command. During the data phase, $\overline{C/BE}(3:0)$ are used as Byte Enables. The Byte Enables<br>are valid for the entire data phase and determine<br>which byte lanes carry meaningful data. $\overline{C/BE0}$<br>applies to byte 0 (lsb) and $\overline{C/BE3}$ applies to byte 3<br>(msb).<br>When MUNICH128X is Master, $\overline{C/BE}(3:0)$ are<br>outputs.<br>When MUNICH128X is Slave, $\overline{C/BE}(3:0)$ are inputs.<br>$\overline{C/BE}(3:0)$ is sampled on the rising edge of CLK. |

| 28                                                                                     | PAR               | t/s  | Parity<br>PAR is even parity across AD(31:0) and C/BE(3:0).<br>PAR is stable and valid one clock after the address<br>phase. PAR has the same timing as AD(31:0) but<br>delayed by one clock.<br>When MUNICH128X is Master, PAR is output during<br>address phase and write data phases.<br>When MUNICH128X is Slave, PAR is output during<br>read data phases. Parity errors detected by the<br>MUNICH128X are indicated on PERR output. PAR is<br>sampled on the rising edge of CLK.                                                                                                                                    |

| Table 2-5 | Pin Descriptions by Functional Block: PCI Interface (cont | 'd) |

|-----------|-----------------------------------------------------------|-----|

|-----------|-----------------------------------------------------------|-----|

| Pin No. | Symbol | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19      | FRAME  | s/t/s | Frame<br>FRAME indicates the beginning and end of an access.<br>FRAME is asserted to indicate a bus transaction is<br>beginning. While FRAME is asserted, data transfers<br>continue. When FRAME is deasserted, the<br>transaction is in the final phase.<br>When MUNICH128X is Master, FRAME is an output.<br>When MUNICH128X is Slave, FRAME is an input.<br>FRAME is sampled on the rising edge of CLK.                                                                                                                                                                                                                            |

| 20      | IRDY   | s/t/s | Initiator Ready<br>IRDY indicates the bus master's ability to complete the<br>current data phase of the transaction. It is used in<br>conjunction with TRDY. A data phase is completed on<br>any clock where both IRDY and TRDY are sampled<br>asserted. During a write, IRDY indicates that valid<br>data is present on AD(31:0). During a read, it indicates<br>the master is prepared to accept data. Wait cycles are<br>inserted until both IRDY and TRDY are asserted<br>together.<br>When MUNICH128X is Master, IRDY is an output.<br>When MUNICH128X is Slave, IRDY is an input.<br>IRDY is sampled on the rising edge of CLK. |

| 21      | TRDY   | s/t/s | Target ReadyTRDY indicates a slave's ability to complete thecurrent data phase of the transaction. During a read,TRDY indicates that valid data is present on AD(31:0).During a write, it indicates the target is prepared toaccept data.When MUNICH128X is Master, TRDY is an input.When MUNICH128X is Slave, TRDY is an output.TRDY is sampled on the rising edge of CLK.                                                                                                                                                                                                                                                           |

| 23      | STOP   | s/t/s | STOPSTOP is used by a slave to request the current masterto stop the current bus transaction.When MUNICH128X is Master, STOP is an input.When MUNICH128X is Slave, STOP is an output.STOP is sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 2-5 | Pin Descriptions by Functional Block: PCI Interface (c | cont'd) |  |

|-----------|--------------------------------------------------------|---------|--|

|-----------|--------------------------------------------------------|---------|--|

| Pin No. | Symbol | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IDSEL  | I     | Initialization Device Select<br>When MUNICH128X is slave in a transaction, if IDSEL<br>is active in the address phase and C/BE(3:0) indicates<br>a Config read or write, the MUNICH128X assumes a<br>read or write to a configuration register. In response,<br>the MUNICH128X asserts DEVSEL during the<br>subsequent CLK cycle.<br>IDSEL is sampled on the rising edge of CLK.                                                                                                                                                                            |

| 22      | DEVSEL | s/t/s | Device Select<br>When activated by a slave, it indicates to the current<br>bus master that the slave has decoded its address as<br>the target of the current transaction. If no bus slave<br>activates DEVSEL within six bus CLK cycles, the<br>master should abort the transaction.<br>When MUNICH128X is Master, DEVSEL is input. If<br>DEVSEL is not activated within six clock cycles after<br>an address is output on AD(31:0), the MUNICH128X<br>aborts the transaction and gen <u>erates an</u> INTA.<br>When MUNICH128X is Slave, DEVSEL is output. |

| 26      | PERR   | s/t/s | Parity Error<br>When activated, indicates a parity error over the<br>AD(31:0) and C/BE(3:0) signals (compared to the<br>PAR input). It has a delay of one CLK cycle with<br>respect to AD and C/BE(3:0) (i.e., it is valid for the<br>cycle immediately following the corresponding PAR<br><u>cycle</u> ).<br>PERR is asserted relative to the rising edge of CLK.                                                                                                                                                                                          |

| 27      | SERR   | o/d   | <b>System Error</b><br>The MUNICH128X asserts this signal to indicate a<br><u>fatal system error</u> .<br>SERR is sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 147     | REQ    | t/s   | Request<br>Used by the MUNICH128X to request control of the<br>PCI.<br>REQ is sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 2-5 | Pin Descriptions by Functional Block: PCI Interface (cor | nťd) |

|-----------|----------------------------------------------------------|------|

|-----------|----------------------------------------------------------|------|

| Pin No. | Symbol | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 146     | GNT    | t/s         | <b>Grant</b><br>This signal is asserted by the arbiter to grant control of<br>the PCI to the MUNICH128X in response to a bus<br>request via REQ. After GNT is asserted, the<br>MUNICH128X will begin a bus transaction only after<br>the current bus Master has deasserted the FRAME<br>signal.<br>GNT is sampled on the rising edge of CLK.                                                               |

| 145     | CLK    | I           | <b>Clock</b><br>Provides timing for all PCI transactions. Most PCI<br>signals are sampled or output relative to the rising<br>edge of CLK. The maximum CLK frequency is<br>33 MHz.                                                                                                                                                                                                                         |

| 142     | RST    | 1           | <b>Reset</b><br>An active RST signal brings all PCI registers,<br>sequencers and signals into a consistent state. All PCI<br>output signals are driven to their initial state.                                                                                                                                                                                                                             |

| 57      | INTA   | O (o/<br>d) | Interrupt Request<br>When an interrupt status is active and unmasked, the<br>MUNICH128X activates this open-drain output.<br>Examples of interrupt sources are transmission/<br>reception error, completion of transmit or receive<br>packets etc. The MUNICH128X deactivates INTA<br>when the global interrupt status register STAT is read.<br>INTA is activated/deactivated asynchronous to the<br>CLK. |

# **Pin Descriptions**

| Table 2-6                                                           | Pin Descriptions by Functional Block:<br>DEMUX Interface (additional signals to PCI Interface) |      |                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                                             | Symbol                                                                                         | Туре | Description                                                                                                                                                                                                                                                                                      |

| 122, 123                                                            | DPCI(1:0)                                                                                      | 1    | PCI/De-multiplexed Mode selectDPCI(1:0) = $00_2$ : PCI ModeDPCI(1:0) = $01_2$ : reservedDPCI(1:0) = $10_2$ : PCI/De-multiplexed ModeDPCI(1:0) = $11_2$ : reservedPins DPCI(1:0) should be connected to $V_{DD3}/V_{ss}$ toachieve the appropriate mode selection.                                |

| 5861,<br>6670,<br>7376, 79,<br><b>124</b> 126,<br>129133,<br>138141 | A(27:2)                                                                                        | I/O  | <ul> <li>DEMUX Address Bus These pins provide the address bus for the De-<br/>multiplexed Interface, when DPCI(1:0) = 10<sub>2</sub>. </li> <li>Note: Pin 124 'A27' provides a buffered PCI clock output<br/>signal if configured in <u>PCI operation mode</u><br/>(DPCI(1:0) = '00').</li></ul> |

| 80                                                                  | W/R                                                                                            | I/O  | Write/ReadThis signal distinguishes write and read operations in<br>the De-multiplexed mode. It is tristate when the<br>MUNICH128X is in PCI mode.A Pull-Up resistor to $V_{DD3}$ is recommended if De-<br>multiplexed mode is not used.                                                         |

25

| Pin No.                                                                                                                    | Symbol           | Туре | Description                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 10, 18,<br>25, 32, 38,<br>44, 50, 56,<br>63, 65, 72,<br>78, 88, 101,<br>104, 118,<br>128, 135,<br>137, 144,<br>151, 158 | V <sub>ss</sub>  | -    | Ground (0 V)<br>All pins must have the same reference level.                                                                                                                                                                                |

| 3, 9, 17, 24,<br>31, 37, 43,<br>49, 55, 62,<br>64, 71, 77,<br>87, 102,<br>103, 117,<br>127, 134,<br>136, 143,<br>150, 157  | V <sub>DD3</sub> | -    | Supply Voltage (3.3 V ± 0.3 V)<br>All pins must have the same reference level.                                                                                                                                                              |

| 15, 16                                                                                                                     | V <sub>DD5</sub> | -    | Supply Voltage<br>These pins MUST be connected to 5 V supply.<br>The MUNICH128X uses 3.3 V I/O pads that always<br>require additional 5 V supply.<br>The 5 V power supply allows the MUNICH128X I/O<br>pads to provide 5 V input tolerance. |

Table 2-7

Pin Descriptions by Functional Block: Power Supply

| Table 2-8 Pin Descriptions by Functional Block: Test Interf |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Pin No. | Symbol | Туре | Description                                                                                                          |

|---------|--------|------|----------------------------------------------------------------------------------------------------------------------|

| 115     | ТСК    | I    | JTAG Test Clock<br>A Pull-Up resistor to V <sub>DD3</sub> is recommended if<br>boundary scan unit is not used.       |

| 116     | TMS    | I    | JTAG Test Mode Select<br>A Pull-Up resistor to V <sub>DD3</sub> is recommended if<br>boundary scan unit is not used. |

| 121     | TDI    | 1    | JTAG Test Data Input<br>A Pull-Up resistor to V <sub>DD3</sub> is recommended if<br>boundary scan unit is not used.  |

| 120     | TDO    | 0    | JTAG Test Data Output                                                                                                |

| 119     | TRST   | I    | JTAG Reset<br>TRST should be connected to VSS if boundary<br>scan unit is not used.                                  |

# 3 Functional Description

# 3.1 Functional Overview

The MUNICH128X provides four independent "cores" as well as global functional blocks (see **Figure 3-1**).

# 3.2 Block Diagram

Figure 3-1 Block Diagram

# 3.3 Functional Blocks

Each core consists of dedicated circuitry: Serial PCM Interface Controller, Configuration and State RAM (CSR), 24/32-channel HDLC Controller with internal Transmit and Receive Buffers, 64-Channel DMA Controller, and Register Set.

# 3.3.1 Serial PCM Interface Controller

This block controls both Parallel–to-Serial (Tx) and Serial-to-Parallel (Rx) conversion and PCM timing. Additionally, this block controls the multiplexing of channels through the HDLC controller, as well as switching for the test loops.

# 3.3.2 Configuration and State RAM (CSR)

This block contains internal RAM which maintains the state of each channel. The Multiplex Control Block of the Serial PCM Interface Controller handles the switching of the CSR information into and out of the 24/32-channel HDLC Controller.

# 3.3.3 24/32-channel HDLC Controller

The HDLC Controller performs protocol processing for each channel independently, based on the CSR information for each channel.

# 3.3.3.1 Tx Block

# Transmit Buffer (TB)

The Tx Block of the HDLC Controller contains a 1024 byte buffer (TB) which may be allocated to all 32 channels of one cove equally (i.e., 2-DWords per channel) or may be allocated based on superchannel considerations (e.g., 8–DWords per channel for 8 channels).

# HDLC Protocol

Bit stuffing, flag generation, flag stuffing and adjustment, and CRC generation (either 16bit or 32-bit) are performed.

# V.110 and V.30 Protocol

Bit framing from 600 bit/s to 38.4 Kbit/s, automatic generation of the synchronization pattern, generation of loss of synchronization, programmable E/SX bits (including during run-time) are performed.

#### **Transparent Mode A**

This mode supports slot synchronous, transparent transmission without frame structure. It provides flag generation, flag stuffing, flag generation in the abort case with programmable flag, and synchronized data transfer for fractional T1/E1 PRI applications.

# **Transparent Mode B**

This mode supports transparent transmission in frames delimited by  $00_{H}$  flags, shared closing and opening flag, flag stuffing and flag generation in the abort case.

#### **Transparent Mode R**

This mode supports transparent transmission with GSM 08.60 frame structure with automatic  $0000_{\rm H}$  flag generation and support of 40, 39.5, and 40.5 octet frames.

#### **Protocol Independence**

Channel inversion (data, flags, idle code) follows the format conventions as in CCITT Q.921.

# 3.3.3.2 Rx Block

# Receive Buffer (RB)

The Rx Block of the HDLC Controller contains a 1024 byte buffer (RB) which is allocated to channels via requests from the protocol controller, as determined by the received data for each channel.

# HDLC Protocol

Flag detection (supports multiple flags between packets or a single flag shared as a closing flag and an opening flag between packets), abort character detection, idle code detection, zero-bit detection and deletion, packet length count, and CRC checking (either 16-bit or 32-bit) are performed.

#### V.110 and V.30 Protocol

Bit framing from 600 bit/s to 38.4 Kbit/s, automatic synchronization of the synchronization pattern, detection of loss of synchronization, programmable E/SX bits (including during run–time) are performed.

#### Transparent Mode A

Mode A supports slot synchronous transparent reception without frame structure. It provides flag detection, flag extraction and synchronized data transfer for fractional T1/ E1 PRI applications.

# Transparent Mode B

This mode supports transparent reception in frames delimited by  $00_{H}$  flags. Sharing closing flag and opening flag, and flag detection.

#### **Transparent Mode R**

This mode supports transparent reception with GSM 08.60 frame structure with automatic  $0000_{H}$  flag detection. Support of 40, 39.5, and 40.5 octet frames, and error detection (non–octet frame contents, short frame, long frame).

#### **Protocol Independence**

Channel inversion (data, flags, idle code) follows the format conventions as in CCITT Q.921, data overflow and underflow detection.

# 3.3.3.3 64-channel DMA Controller Block

This block controls memory address calculation, buffer management (including linkedlists) and interrupt processing. The 24/32-channel HDLC Controller has a dedicated DMA channel for each channel and direction. During run-time, the DMA Controller performs operations with host memory primarily as a bus master. This block provides 32 input and 32 output channels.

# 3.3.3.4 Register Set

This block provides configuration and control of the Serial PCM Interface Controller, the HDLC Controller and the DMA Controller. Also, a shared status register STAT provides status and interrupt information associated with each of the four cores.

# 3.4 Global Functional Blocks

The MUNICH128X provides global functional blocks for the Internal Bus, Arbiter, and 32 Bit / 33 MHz PCI 2.1 Interface as well as De-multiplexed Bus Interface Controller.

#### 3.4.1 Internal Bus

This block of the MUNICH128X interfaces the Bus Interface Controller to the four DMA Controllers. This is a 33 MHz, 32 Bit demultiplexed bus that operates in a synchronous, non–burst manner for data transfers and operates in a synchronous burst manner for descriptor transfers.

#### 3.4.2 Arbiter

The Arbiter provides access control of the Internal Bus. A "round-robin" Arbiter is used which provides "fairness" for the four master DMA controllers.

# 3.4.3 32 Bit / 33 MHz Bus Interface Controller

The MUNICH128X may be configured either for 32 Bit / 33 MHz PCI bus operation or for a 32 Bit / 33 MHz De-multiplexed bus interface. The MUNICH128X input pins DPCI(1:0) are used to select the desired configuration.

The De-multiplexed bus interface is a synchronous interface very similar to the PCI interface with the following exceptions:

- 1. The W/ $\overline{R}$  input/output signal replaces the function of the PCI command nibble of the C/BE(3:0) bit field.

- Note, that in DEMUX mode as in PCI mode the MUNICH128X provides only the first address of a Master burst read or write transaction. If burst transactions are not supported by the local bus environment, burst capability can be disabled by bit DBE in the global configuration register (CONF).

# 3.5 System Integration

The MUNICH128X provides protocol processing and host memory buffer management for four independent T1/E1 PRI ports. As such, the MUNICH128X fits into a system between the framer or LIU/framer devices (e.g., the Siemens FALC<sup>®</sup>54/FALC<sup>®</sup>54-LH transceiver) and the host bus (e.g. PCI Bus), as illustrated in **Figure 3-1**.

The MUNICH128X provides four independent Serial PCM ports which connect directly into the framer devices. In PCI based systems a dedicated microcontroller or PCI bridge chip is necessary to configure the framer or LIU/framer devices.

Additionally, the MUNICH128X provides a PCI 2.1 interface which connects directly to the system PCI bus. Optionally, this bus can be configured in De-multiplexed Mode.

Figure 3-1 System Integration of the MUNICH128X in PCI-Based System

Figure 3-2 System Integration of the MUNICH128X in De-multiplexed System

#### **Operational Description**

# 4 **Operational Description**

# 4.1 **Operational Overview**

The MUNICH128X is a "channelized" WAN protocol controller that performs protocol processing on up to 128 full duplex serial PCM channels. It performs HDLC-based layer 2 protocol formatting and deformatting, as well as rate adaptation, for each of the 128 channels independently.

The MUNICH128X provides dedicated registers for each of the four HDLC controllers, with each set similar to the "core" registers of the MUNICH32X. Software developed for the "core" of the MUNICH32X requires minimal modification to run optimally on the MUNICH128X. The architecture of the register sets allows any number of HDLC controllers within an MUNICH128X device to operate with host software images that differ only in their offset from the PCI base address and their pointers into host memory.

Host software sets the operating mode, rate adaptation method and time slot assignment of each channel by configuring "blocks" (CCBs) within host memory.

During "run-time" the MUNICH128X performs all data and descriptor transfers as a bus master. Additionally, host software may access any register of a particular HDLC Controller within the MUNICH128X, with the device acting as a bus slave.

The MUNICH128X provides a single Status Register, which maintains information of all interrupt events for the controller.

# 5 Electrical Characteristics

### 5.1 Important Electrical Requirements

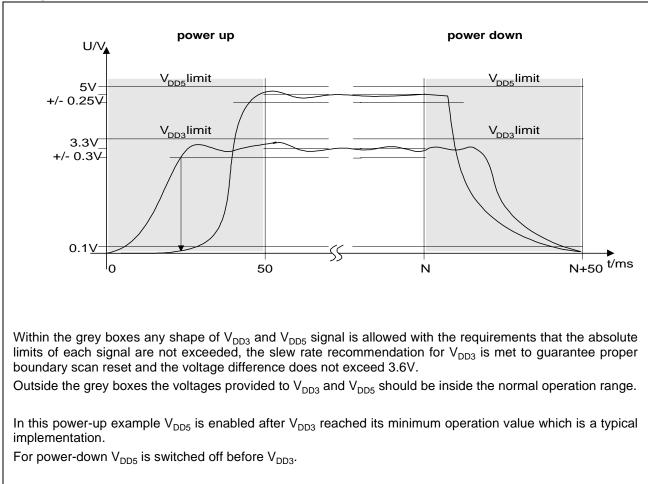

$V_{DD5} = 5.0 V \pm 0.25 V$   $V_{DD5 max} = 5.25 V$

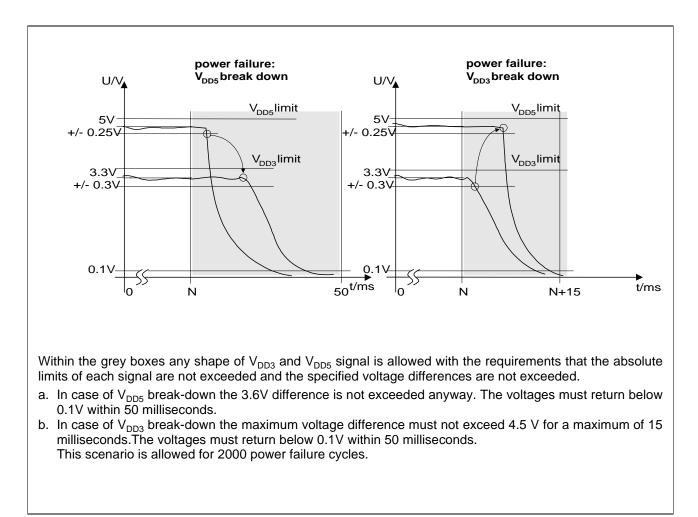

During all MUNICH128X power-up and power-down situations the difference

$|V_{\text{DD5}}-V_{\text{DD3}}|$  may not exceed 3.6V. The absolute maximums of  $V_{\text{DD5}}$  and  $V_{\text{DD3}}$  should never be exceeded.

Figure 5-1 shows that both  $V_{DD3}$  and  $V_{DD5}$  can take on any time sequence not exceeding a voltage difference of 3.6V, for up to 50 milliseconds at power-up and powerdown.Within 50 milliseconds of power-up the voltages must be within their respective absolute voltage limits. At power-down, within 50 milliseconds of either voltage going outside its operational range, the voltage difference should not exceed 3.6V and both voltages must be returned below 0.1V:

#### Figure 5-1 Power-up and Power-down scenarios

Similar criteria also apply to power down in case of power failure situations:

Figure 5-2 Power-Failure scenarios

#### 5.2 Absolute Maximum Ratings

#### Table 5-1 Absolute Maximum Ratings

| Parameter                                                    | Symbol           | Limit    | Values                 | Unit |

|--------------------------------------------------------------|------------------|----------|------------------------|------|

|                                                              |                  | min.     | max.                   |      |

| Ambient temperature under bias<br>PEB<br>PEF                 | T <sub>A</sub>   | 0<br>-40 | 70<br>85               | °C   |

| Junction temperature under bias                              | TJ               |          | 125                    | °C   |

| Storage temperature                                          | T <sub>stg</sub> | - 65     | 125                    | °C   |

| Voltage at any pin with respect to ground                    | Vs               | -0.4     | V <sub>DD5</sub> + 0.4 | V    |

| ESD robustness <sup>1)</sup><br>HBM: 1.5 k $\Omega$ , 100 pF | $V_{ESD,HBM}$    |          | 1000                   | V    |

<sup>1)</sup> According to MIL-Std 883D, method 3015.7 and ESD Ass. Standard EOS/ESD-5.1-1993. The RF Pins 20, 21, 26, 29, 32, 33, 34 and 35 are not protected against voltage stress > 300 V (versus V<sub>S</sub> or GND). The high frequency performance prohibits the use of adequate protective structures.

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 5.3 Thermal Package Characteristics

#### Table 5-2Thermal Package Characteristics

| Parameter          | Symbol                | Value                 | Unit |      |

|--------------------|-----------------------|-----------------------|------|------|

| Thermal Package Re |                       |                       |      |      |

| Airflow:           | Ambient Temperature:  |                       |      |      |

| without airflow    | T <sub>A</sub> =+25°C | θ <sub>JA(0,25)</sub> | 29   | °C/W |

## 5.4 Operating Range

| Parameter                         | Symbol          | Limit Values |          | Unit | Test Condition |

|-----------------------------------|-----------------|--------------|----------|------|----------------|

|                                   |                 | min.         | max.     |      |                |

| Ambient temperature<br>PEB<br>PEF | T <sub>A</sub>  | 0<br>-40     | 70<br>85 | °C   |                |

| Supply voltage VDD3               | $V_{DD3}$       | 3.0          | 3.6      | V    |                |

| Supply voltage VDD5               | $V_{DD5}$       | 4.75         | 5.25     | V    |                |

| Ground                            | V <sub>SS</sub> | 0            | 0        | V    |                |

Note: In the operating range, the functions given in the circuit description are fulfilled.

### 5.5 DC Characteristics

#### a) Non-PCI Interface Pins

Table 5-3Non-PCI Interface Pins $T_A = 0$  to + 70°C;  $V_{DD5} = 5$  V  $\pm$  5%,  $V_{DD3} = 3.3$  V  $\pm$  0.3 V,  $V_{SS} = 0$  V

| Parameter                                                         |                          | Symbo                              | o Limit Values |                     | Unit | Test Condition                                                                           |

|-------------------------------------------------------------------|--------------------------|------------------------------------|----------------|---------------------|------|------------------------------------------------------------------------------------------|

|                                                                   |                          | I                                  | min.           | max.                |      |                                                                                          |

| L-input volta                                                     | age                      | $V_{IL}$                           | - 0.4          | 0.8                 | V    |                                                                                          |

| H-input volta                                                     | age                      | $V_{IH}$                           | 2.0            | $V_{\rm DD5}$ + 0.4 | V    |                                                                                          |

| L-output vol                                                      | tage                     | V <sub>QL</sub>                    |                | 0.45                | V    | $I_{QL}$ = 7 mA<br>(pin TXD)<br>$I_{QL}$ = 2 mA<br>(all others / non-PCI)                |

| H-output vo                                                       | ltage                    | $V_{QH}$                           | 2.4            |                     | V    | <i>I</i> <sub>QH</sub> = - 400 μA                                                        |

| Power                                                             | operational              | I <sub>CC3</sub>                   |                | < 300               | mA   | $V_{\rm DD3} = 3.3  \rm V,$                                                              |

| supply<br>current                                                 | powerdown<br>(no clocks) | I <sub>CC3</sub>                   |                | < 5                 | mA   | $V_{DD5} = 5.0 V,$<br>inputs at 0 V/ $V_{DD3}$ ,<br>no output loads                      |

|                                                                   | operational              | I <sub>CC5</sub>                   |                | < 1                 | mA   | $V_{\rm DD3} = 3.3  \rm V,$                                                              |

|                                                                   | powerdown<br>(no clocks) | I <sub>CC5</sub>                   |                | < 1                 | mA   | $V_{DD5} = 5.0 V,$<br>inputs at 0 V/ $V_{DD3}$ ,<br>no output loads                      |

| Peak Power supply<br>current during<br>RAM initialization process |                          | I <sub>CC3Peak</sub>               |                | < 700               | mA   | $V_{\rm DD3} = 3.3 \text{ V},$<br>$V_{\rm DD5} = 5.0 \text{ V},$                         |

|                                                                   |                          | I <sub>CC5Peak</sub>               |                | < 10                | mA   | inputs at 0 V/V <sub>DD3</sub> ,<br>no output loads,<br>300 PCI clocks after<br>power-up |

| Input leakag<br>Output leaka                                      | -                        | I <sub>LI</sub><br>I <sub>LQ</sub> |                | 10                  | μA   | 0 V < $V_{\rm IN}$ < $V_{\rm DD}$ to 0 V<br>0 V < $V_{\rm OUT}$ < $V_{\rm DD}$ to 0 V    |

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25 \,^{\circ}C$  and the given supply voltage.

Note: The electrical characteristics described in **section 5.2** also apply here!

### b) PCI Pins

According to the PCI specification V2.1 from June 1, 1995 (Chapter 4: Electrical Specification for 5 V signalling)

Note: According the electrical characteristics all DEMUX Interface pins (DPCI(1:0),  $A(27:2), W/\overline{R}$ ) are treated as PCI Interface pins.

#### 5.6 Capacitances

#### a) Non-PCI Interface Pins

# Table 5-4Non-PCI Interface Pins $T_A = 25^{\circ}$ C; $V_{DD5} = 5 V \pm 5\%$ , $V_{DD3} = 3.3 V \pm 0.3 V$ , $V_{SS} = 0 V$

|                    |                  |              |      | •    | -              |

|--------------------|------------------|--------------|------|------|----------------|

| Parameter          | Symbol           | Limit Values |      | Unit | Test Condition |

|                    |                  | min.         | max. |      |                |

| Input capacitance  | C <sub>IN</sub>  | 1            | 5    | pF   |                |

| Output capacitance | C <sub>OUT</sub> | 5            | 10   | pF   |                |

| I/O-capacitance    | C <sub>IO</sub>  | 6            | 15   | pF   |                |

### b) PCI Pins

According to the PCI specification V2.1 from June 1, 1995 (Chapter 4: Electrical Specification for 5 V signalling)

Note: According the electrical characteristics all DEMUX Interface pins DPCI(1:0),  $A(27:2), W/\overline{R}$ ) are treated as PCI Interface pins.

### 5.7 AC Characteristics

#### a) Non-PCI Interface Pins

$T_{\rm A}$  = 0 to + 70°C;  $V_{\rm DD5}$  = 5 V ± 5%;  $V_{\rm DD3}$  = 3.3 V ± 0.3 V

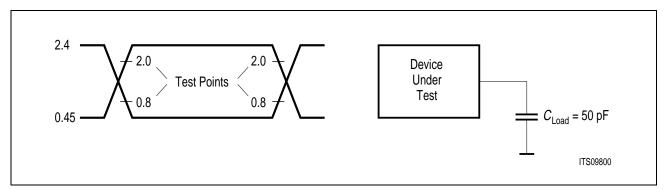

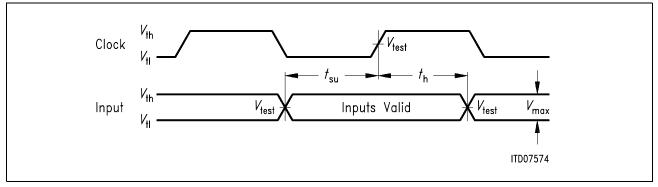

Inputs are driven to 2.4 V for a logical "1" and to 0.4 V for a logical "0". Timing measurements are made at 2.0 V for a logical "1" and at 0.8 V for a logical "0".

The AC testing input/output waveforms are shown below.

### b) PCI Pins

According to the PCI specification V2.1 from June 1, 1995 (Chapter 4: Electrical Specification for 5 V signalling)

Note: According the electrical characteristics all DEMUX Interface pins DPCI(1:0), A(27:2),  $W/\overline{R}$ ) are treated as PCI Interface pins.

### 5.7.1 PCI Bus Interface Timing

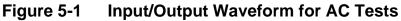

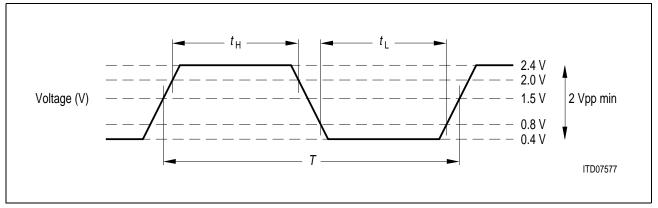

The AC testing input/output waveforms are shown in figures 5-2 and 5-3 below.

Figure 5-3 PCI Input Timing Measurement Waveforms

| Table 5-5 | PCI Input and Output Measurement Conditions |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

| Symbol            | Value | Unit |  |

|-------------------|-------|------|--|

| $V_{th}$          | 2.4   | V    |  |

| V <sub>tl</sub>   | 0.4   | V    |  |

| V <sub>test</sub> | 1.5   | V    |  |

| V <sub>max</sub>  | 2.0   | V    |  |

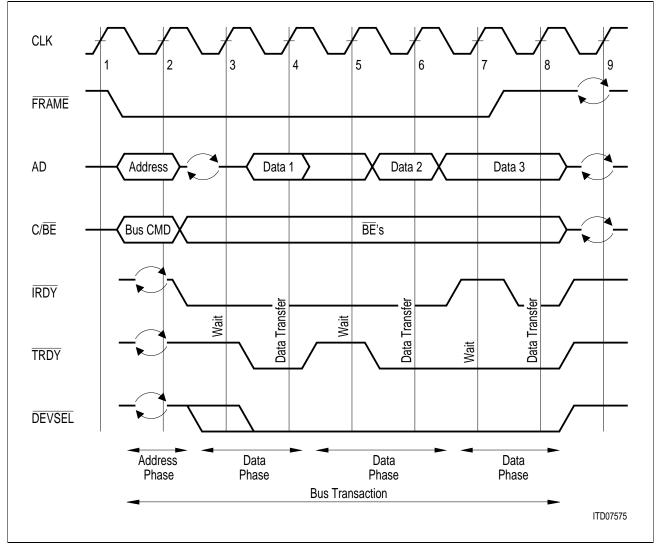

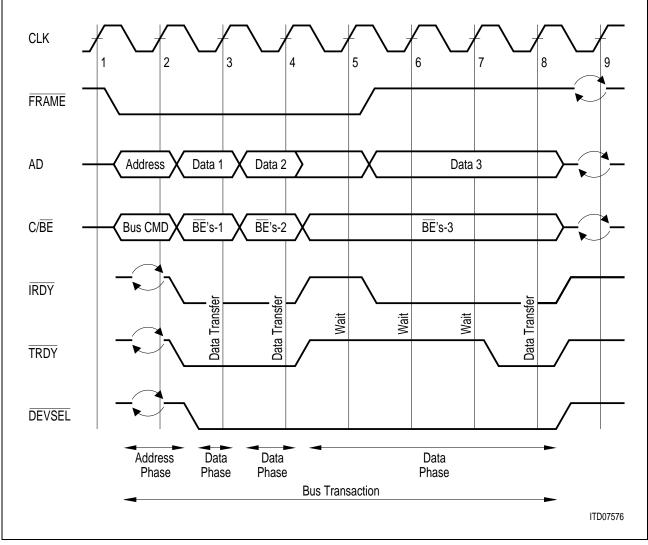

The timings below show the basic read and write transaction between an initiator (Master) and a target (Slave) device. The MUNICH128X is able to work both as master and slave.

As a master the MUNICH128X reads/writes data from/to host memory using DMA and burst. The slave mode is used by an CPU to access the MUNICH128X PCI Configuration Space and the on-chip registers.

### 5.7.1.1 PCI Read Transaction

<u>The transaction starts with an address phase which occurs during the first cycle when</u> FRAME is activated (clock 2 in **figure 5-4**). During this phase the <u>bus master</u> (initiator) outputs a valid address on AD(31:0) and a valid bus command on C/BE(3:0). The first clock of the first data phase is clock 3. During the data phase C/BE indicate which byte lanes on AD(31:0) are involved in the current data phase.